Multiboot是指多镜像启动,比如在FPGA的加载flash里面存放2个或者多个FPGA的配置文件,每个配置文件都可以单独完成FPGA的逻辑配置

KR260 DPU配置教程1

作者:Chen Shaoyi,AMD工程师;来源:AMD开发者社区

官网上没有提供KR260的DPU预配置工程。在这篇博客中,我们将为 KR260 Vitis 加速平台创建硬件设计。 我们将从KR260预设文件开始,添加平台所需的外设并对其进行配置。 一切设置完毕后,我们将把硬件设计导出到XSA。

创建名为kr260_platform的Platform

Create Project > Next

Project name: kr260_platform > Next

勾选 "Project is an extensible Vitis platform" > Next

开发板选择Boards > KR260 > Next > Finish

如果没有安装KR260,需要先安装KR260

创建一个Block Design

Create Block Design > OK

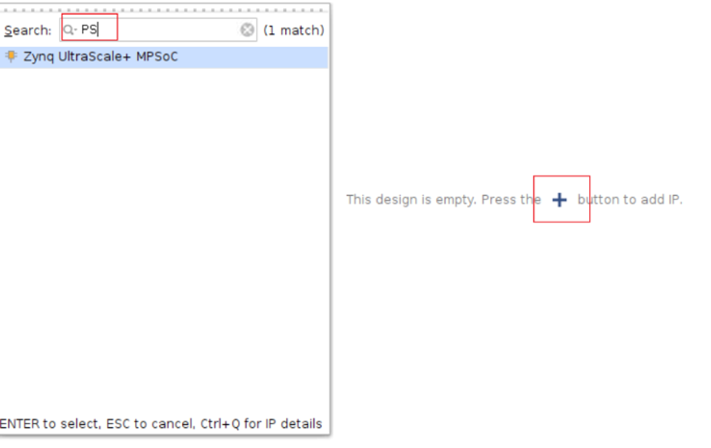

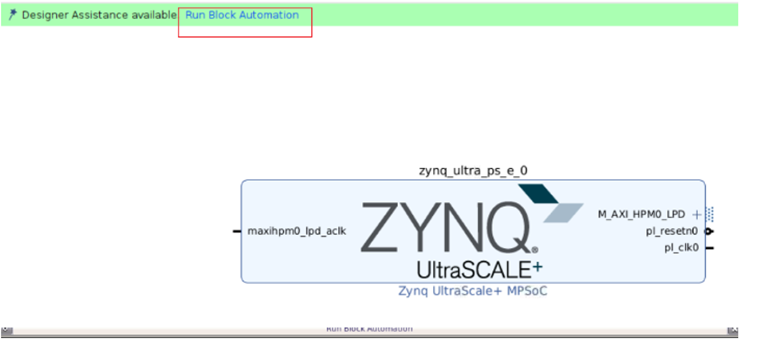

Add PS > Run Block Automation > Apply Board Preset > OK

在此阶段,Vivado自动添加了 Zynq UltraScale+ MPSoC,并应用了 KR260 的所有板卡预设选项。 预设选项包括 MPSoC PS 模块配置和引脚分配。

创建时钟和复位

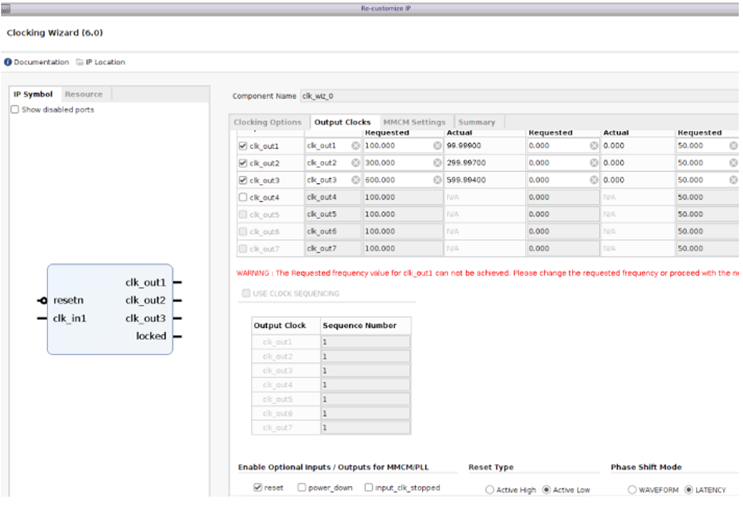

Add a Clocking Wizard

使能Platform的AXI接口

使能PS的AXI Master接口

使能来自AXI Interconnect的AXI Master interfaces

使能来自PS的AXI Slave interfaces来允许kernels 连接 DDR 内存

导出XSA

点击 Validate Design 按钮来确认 block design 设计有效。在这个过程中Vivado会报告一个critical warning,这是因为 /axi_intc_0/intr 没有被连接。因为v++链接器会将中断连接到这个端口上,所以这个警告可以被忽略。

为 block design创建一个module wrapper

生成设计

导出 platform

. Name: kv260_hardware_platform

. Vendor: xilinx

. Board: kv260

. Version: 0.0

. Description: This platform provides high PS DDR bandwidth and three clocks.

参考链接:https://github.com/Xilinx/Vitis-Tutorials/tree/2022.2/Vitis_Platform_Cre...

最新文章

Vitis AI 工具概述 |

基于Zynq UltraScale+ MPSoC高性能EtherCAT主站方案 |

AMD Xilinx MPSoC VCU 使用要点 |

Multi-Scaler IP的linux示例以及debug(下) |

如何在petalinux环境下使用python脚本实现opencv显示USB camera图像 |

用最新视频AI 解决方案解决当今视频分析五大难题 |